Metal filling and slotting for metal density rules. It consists of Operating Conditions Wire Load Models and System Interface requirements.

Ardublock Is A Graphical Programming Environment To Make Programming Physical Computing With Arduino As Easy As Drag And Arduino Cool Electronics Gadget Gifts

Repeat the experiment with at least one other volunteer.

. He performed several experiments to test Aristotles theories. The process of identifying an appropriate physical position for each cell in the design is known as placement. Power routing.

Rectifier has evolved design and manufacturing disciplines to validate power MOSFET design ruggedness of EAS rated devices. Application of Design for Manufacturing DFM and Design for Yield DFY rules. This website uses cookies to help provide you with the best possible online experience.

Most parametric statistics like means standard deviations and correlations and every statistic based on these are highly sensitive to outliers. Apart from timing violation there may be issues like IR Drop DRC Violations all these are fixed in this stage and a final layout file free from all the violation is streamed out in GDSII format. Resistor Capacitor AC power source ammeter voltmeter connection wire etc.

Should you drop outliersOutliers are one of those statistical issues that everyone knows about but most people arent sure how to deal with. So the clocks are given higher priority in using routing resources and routed prior to any other net routing. When AC is applied to the parallel RC circuit shown below the capacitor never reaches a final charge and therefore it will always carry some current.

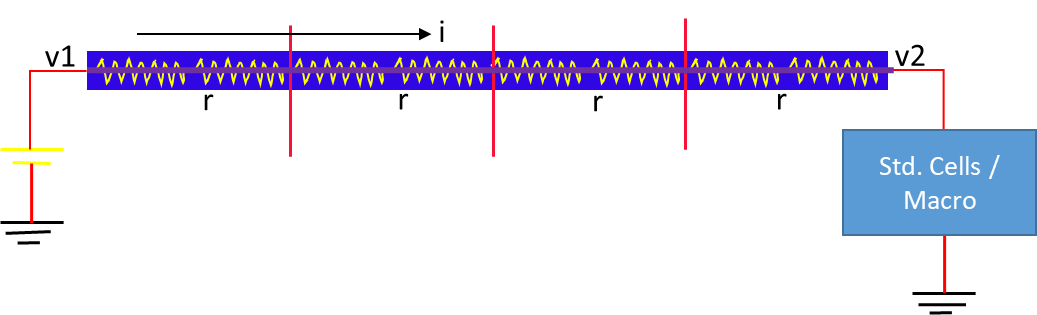

Assume that all the clock blocks are clustered in an area then they will consume more power ie. In this case de cap cells can be used. B Allowable IR drop.

Connect the macro and standard cell power pins to the power rings and staps you have created for the design. To design parallel RC circuit and find out the current flowing thorugh each component. It consists of Process voltage and temperature requirements.

Presently IR uses a three legged approach during design. C Global route congestion. We do not want to upset the skew and delay values for the clock net as much as possible.

Previous Next About ARCHIDEX Held across 4 days annually in Kuala Lumpur Malaysia ARCHIDEX International Architecture Interior Design and Building Exhibition is a Regions Leading Architecture Business Event jointly organised by PAM Pertubuhan Akitek Malaysia or Malaysia Institute of Architects and CIS. In Italy a young scientist and mathematician named Galileo Galilei questioned Aristotles ideas about falling objects. QuizStar is a free online quiz maker that allows you to manage your classes assign quizzes and generate reports of quiz scores and student performance.

MSC Software is a global leader in helping product manufacturers to advance their engineering methods with simulation software and services. A fully-featured 3D modeling tool with photorealistic real-time rendering and an app-free augmented reality experience. 1 Statistically significant samples of prospective designs are tested to failure at test conditions chosen to reach extremes in temperature and current.

Design environment Constraints. The effect each of these can have on the chip. ARCHIDEX is an event of the annual KL Architecture.

These cells aids IR drop issue and remove s glitches in power. A WLM wire load model b NLDM non linear delay. The location has a big impact on the quality of routing in design.

Spotify is all the music youll ever need. D Physical information of the design. What are the different types of delay models.

The point on ruler where it was caught in cm is the recorded measure and can be converted into response time. As legend has it in 1589 Galileo dropped two balls of different masses from a great height near the top of the Tower of Pisa to see which ball hit the ground first. They drew more current which will increase IR drop.

In a design most of the power consumption is done by clock circuits. You might consider letting your volunteers have a rest between trials. Ruler drop test a ruler is dropped between an individuals extended index finger and thumb.

A Blocks JavaScript code editor for the Adafruit Circuit Playground Express. Enjoy ad-free music listening offline playback and more. In the late 1500s CE.

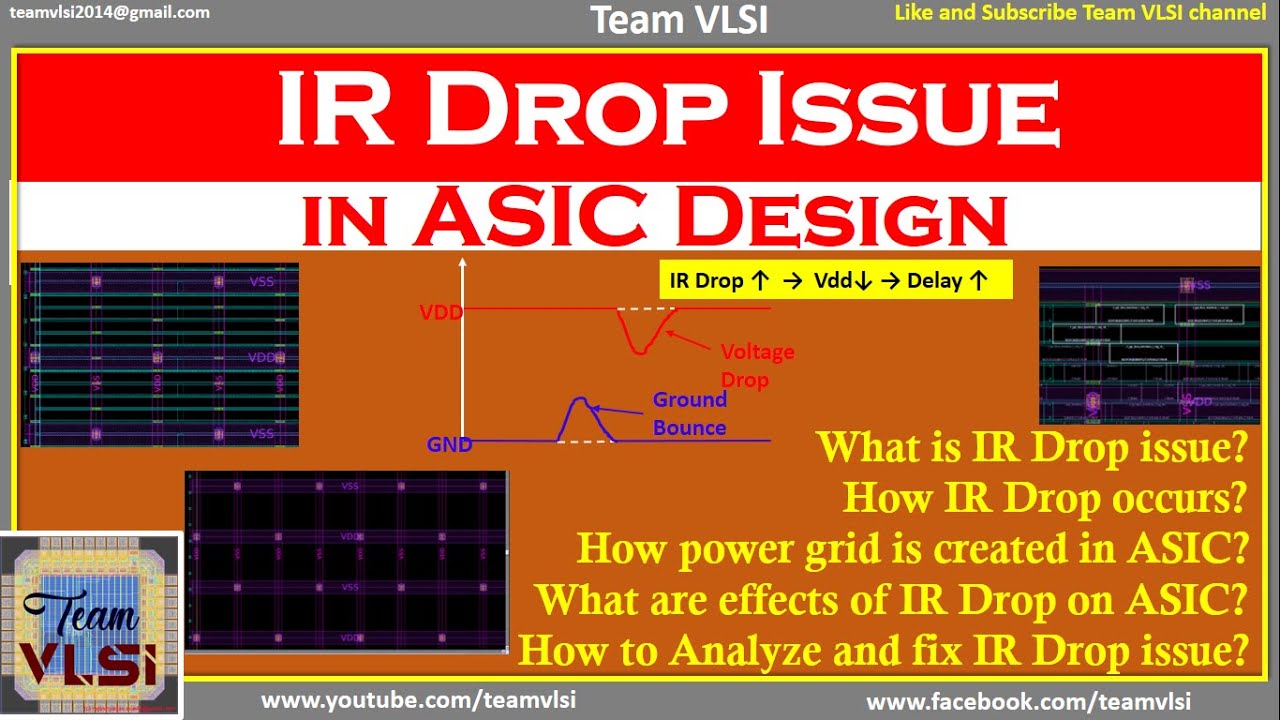

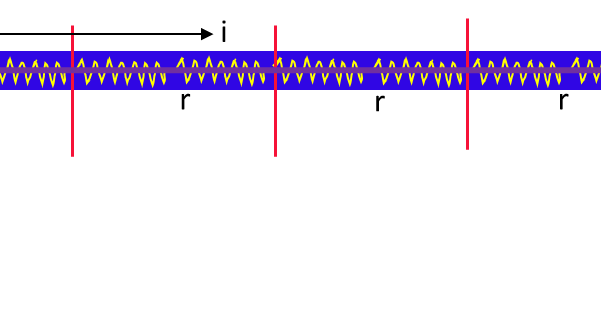

Create and share 3D design content for the web. Please read our Terms Conditions and Privacy Policy for information about. IR Drop Analysis in Physical Design IR Analysis in VLSI I n this article we will discuss what is IR drop in ASIC design Why IR drop issue occurs what are the effects of IR drop and how to analyze and prevent the IR drop issue.

If there are some timing violations in post route design we have a further stage called ECO Engineering Change Order where we can fix the timing violations. When a large number of cells are packed into a compact space the number of routing tracks available for routing is less than the number necessary resulting in design congestion in VLSI. IR Drop and Electromigration Analysis Logic Equivalence Layout Physical Verification Add Sealring 19.

Once the design have been read in you need to define design environment and design constraints. More information about the ruler drop test can be found in reference 14.

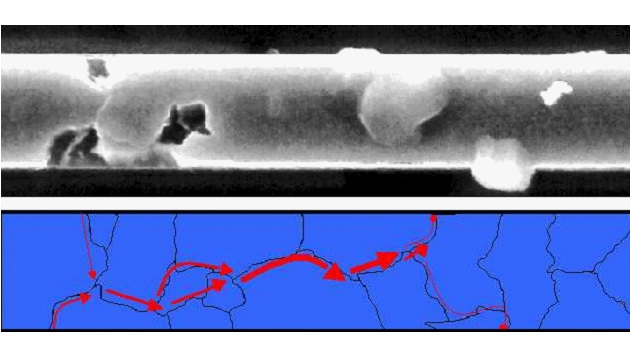

Understanding Electromigration And Ir Drop In Semiconductor Chip Design Challenges And Techniques Ele Times

Physics Games Fun Educational Games Fun Educational Games Physics Educational Games

Physics Current Electricity Physics Formulas Science Physics Mind Maps Advanced Level Physics Study Chemistry Electricity Physics Physics Formulas

Ir Drop Issue In Vlsi What Is Ir Drop In Asic Why Ir Drop Effects Of Ir Drop Youtube

Team Vlsi Ir Drop Analysis In Physical Design Ir Analysis In Vlsi

Fitness Studio Desktop Lightroom Presets Graphic By 3motional Creative Fabrica Photoshop Actions Lightroom Presets Acr Presets

Team Vlsi Ir Drop Analysis In Physical Design Ir Analysis In Vlsi

We Are Hiring Engineers In Semiconductor Domain We Will Hold The Walk In Drive On Saturday September 9 At Our Hyd Engineering We Are Hiring Semiconductor

0 comments

Post a Comment